Über Jahre hinweg wurde Intel vor allem mit verpassten Prozessknoten, verschobenen CPU-Generationen und bombastischen Präsentationen verbunden, bei denen die Folien oft beeindruckender wirkten als die fertigen Produkte. Während die Branche über diese "PowerPoint-Roadmaps" witzelte, hat der Konzern im Hintergrund still und beharrlich an einem anderen Hebel gearbeitet: fortschrittlichem Chip-Packaging.

Genau diese Wette beginnt jetzt Früchte zu tragen. Neue Stellenausschreibungen bei Apple und Qualcomm nennen Intels EMIB- und 3D-Packaging explizit – ein deutliches Zeichen, dass sich hier eine neue Front im Foundry-Geschäft öffnen könnte.

Warum ist Packaging plötzlich so wichtig? Die Antwort liegt im Wandel der Rechenlasten. High-Performance-Computing, KI-Beschleuniger, riesige Cloud-Datenzentren und Premium-Smartphones verlangen heute deutlich mehr Leistung pro Watt und pro Fläche, als ein simples "Shrinken" der Transistoren liefern kann. Der klassische Fortschritt nach dem Gesetz von Moore verlangsamt sich, während die Kosten und Risiken riesiger monolithischer Dies steigen. Die Branche reagiert darauf mit Chiplets: mehreren kleineren, spezialisierten Dies, die in einem einzigen Gehäuse eng gekoppelt werden.

AMD setzt bei Ryzen und EPYC massiv auf Chiplet-Designs, NVIDIA kombiniert große GPUs mit gestapeltem HBM-Speicher und auch Apples M-Serie nutzt komplexe Packaging-Konzepte, um Leistung und Effizienz auszureizen. In all diesen Fällen ist Packaging nicht mehr das "Finish" am Ende der Fertigungslinie, sondern ein zentraler Teil der Architektur. Es entscheidet mit darüber, wie viel Bandbreite zwischen CPU, GPU und Speicher möglich ist und wie kompakt das Gesamtsystem gebaut werden kann.

In diesem Feld war TSMC in den letzten Jahren der Platzhirsch. CoWoS und SoIC wurden zum Quasi-Standard für alle, die beim Performance-Limit mitspielen wollen. Doch der Erfolg hat eine Schattenseite: Die CoWoS-Kapazitäten sind weitgehend durch Großkunden wie NVIDIA und AMD belegt. Für neue oder kleinere Kunden bedeutet das längere Wartezeiten und weniger Verhandlungsmacht. Wenn es praktisch keinen zweiten Anbieter auf vergleichbarem Niveau gibt, sitzt TSMC am längeren Hebel – und genau das versucht Intel zu ändern.

Was EMIB und Foveros technisch besonders macht

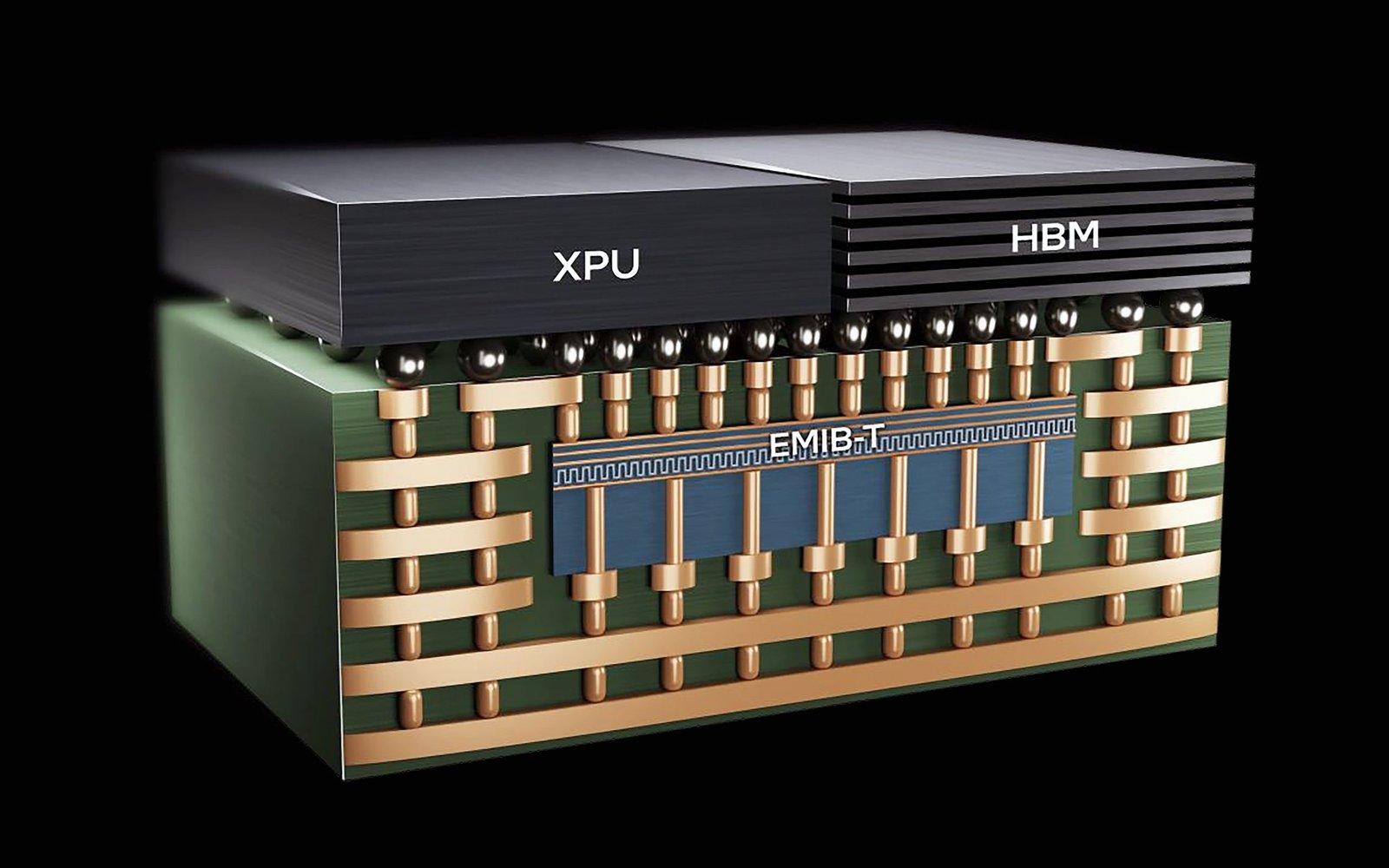

EMIB, ausgeschrieben Embedded Multi-Die Interconnect Bridge, verfolgt einen anderen Ansatz als die klassischen, großen Silizium-Interposer. Statt alle Dies auf eine große Siliziumplatte zu setzen, platziert Intel winzige Silizium-Brücken direkt in der organischen Substrat-Schicht – nur dort, wo extrem breitbandige Verbindungen benötigt werden. CPU-Tiles, GPU-Tiles, I/O-Logik und sogar HBM-Stacks können so mit hoher Dichte verbunden werden, ohne die Kosten und die Komplexität eines riesigen Interposers in Kauf zu nehmen.

Darauf aufbauend kommt Foveros ins Spiel – Intels 3D-Packaging-Technologie. Während EMIB die Kommunikation in der Fläche optimiert, erlaubt Foveros, Dies vertikal übereinander zu stapeln. Über TSVs und immer feinere Metallkontakte entstehen echte 3D-Stacks, bei denen Logik auf Logik oder Speicher auf Logik sitzt. Das Ergebnis sind sehr kompakte Packages mit kurzen Leitungswegen und hoher Energieeffizienz. Foveros Direct treibt dies weiter voran, indem Kupfer-zu-Kupfer-Verbindungen mit sehr kleinem Pitch eingesetzt werden. Kein Wunder, dass selbst NVIDIA-Chef Jensen Huang öffentlich lobende Worte für Foveros gefunden hat – und das, obwohl NVIDIA massiv von TSMCs CoWoS abhängig ist.

Warum Apple und Qualcomm gezielt EMIB-Know-how suchen

Vor diesem Hintergrund wirken die neuen Jobangebote deutlich spannender als gewöhnliche HR-Meldungen. Apple sucht einen DRAM-Packaging-Engineer mit Erfahrung in Technologien wie CoWoS, EMIB, SoIC und PoP. Das heißt nicht automatisch, dass der nächste M-Chip bei Intel vom Band laufen wird. Aber es zeigt, dass Apple intern Kompetenz aufbauen will, um Intels Packaging-Stack wirklich technisch bewerten zu können – nicht nur anhand von Marketing-Slides.

Auch Qualcomm sucht eine leitende Produktmanagement-Rolle im Data-Center-Bereich, bei der explizit Vertrautheit mit EMIB gefragt ist. Genau solche Positionen definieren Roadmaps, verteilen Fertigungsaufträge auf TSMC, Samsung oder potenziell Intel und entscheiden damit über Milliardenbudgets. Solche Anforderungen schreibt man nicht in eine Stellenanzeige, nur um "informiert zu bleiben". Sie deuten darauf hin, dass Intels Packaging ernsthaft als Option auf dem Tisch liegt.

Packaging als attraktivste Einstiegstür zu Intel Foundry

Nüchtern betrachtet ist Packaging aktuell der Teil von Intel Foundry Services, der für externe Kunden am spannendsten wirkt. Bei den modernsten Fertigungsnodes ist Intel noch im Aufholmodus, viele Wafer-Kapazitäten gehen an eigene Produkte. Packaging hingegen ist flexibler: Es kann auf Wafern aus TSMC- oder Samsung-Fabs aufsetzen, es generiert unabhängige Umsätze und erlaubt Kunden, die Zusammenarbeit mit Intel schrittweise aufzubauen, ohne direkt ganze Produktlinien zu verlagern.

Für Schwergewichte wie Apple, Qualcomm oder Broadcom, die massiv in eigene Chips investieren, ist ein zweiter starker Packaging-Partner strategisch extrem wertvoll. Wenn Intel vergleichbare oder sogar bessere Packaging-Lösungen liefern kann und gleichzeitig nicht in denselben CoWoS-Engpass gerät, bröckelt das alte Mantra, niemand wolle mit Intel fertigen. In einem Umfeld, in dem die Alternative oft nur "warten bei TSMC" heißt, bekommt eine glaubwürdige zweite Option automatisch Gewicht.

Skepsis, Optane-Nachwirkungen und das Imageproblem

Allerdings ist die Skepsis gegenüber Intel noch lange nicht verschwunden. Viele erinnern sich an die große Optane-Vision – neue Speicherklasse, revolutionäre Latenzen – und daran, wie leise das Projekt schlussendlich beendet wurde. Das macht einige nervös, wenn es um Ankündigungen zu spektakulären Speicher- und Compute-Modulen auf EMIB-Basis geht.

Hinzu kommt, dass Intel weiterhin beweisen muss, dass das Unternehmen eigene CPU- und GPU-Roadmaps zuverlässig abliefert. Solange es keine prominenten, hochvolumigen Produkte externer Kunden gibt, die auf EMIB und Foveros setzen, werden Kritiker alles leicht als "PowerPoint-Silizium" abtun. Die Lücke zwischen Ankündigung und tatsächlichem Silizium ist ein Reputationsproblem, das Intel nur mit realen Designs schließen kann.

Ein möglicher Wendepunkt im Foundry-Markt

Trotzdem spüren viele Beobachter, dass sich etwas verschiebt. Der Hunger nach KI-Rechenleistung scheint unstillbar, TSMCs CoWoS-Kapazitäten sind stark beansprucht und Chiplet-Designs setzen sich quer durch die Branche durch. Strukturell ist also Platz für einen zweiten ernstzunehmenden Player im High-End-Packaging.

Intel muss TSMC nicht vom Thron stoßen, um erfolgreich zu sein. Es reicht, zu einem verlässlichen, technisch attraktiven "Co-Anbieter" zu werden, sodass große Kunden ihre Risiken und Volumina aufteilen können. Gelingt es Intel, EMIB- und Foveros-Kapazitäten hochzufahren, ordentliche Yields zu halten und wettbewerbsfähige Preise zu bieten, könnte Packaging zum Keil werden, der die Tür zu deutlich größeren Foundry-Deals langsam aufdrückt. Dass Apple und Qualcomm EMIB bereits in ihren Stellenprofilen erwähnen, ist keine Garantie für unmittelbare Design-Wins, aber ein klares Signal: Intel wird in diesem Spiel nicht länger ignoriert. Vielleicht erleben wir gerade den Moment, in dem aus den berüchtigten starken Folien endlich ebenso starkes Silizium wird.