Tachyum sorgt erneut fuer Schlagzeilen – diesmal nicht mit seinen Prodigy-CPUs, sondern mit einem eigenen Speichermodul-Standard namens TDIMM. Auf dem Papier soll TDIMM gleich mehrere heilige Graele moderner Rechenzentren adressieren: deutlich mehr Bandbreite pro Slot, bis zu 1 TB Kapazitaet pro DIMM und spuerbar niedrigere Kosten pro Gigabyte.

Besonders attraktiv klingt das fuer Betreiber grosser KI-Cluster, die heute von Speicherlimitierungen und explodierenden Energiekosten ausgebremst werden.

Was hinter TDIMM steckt

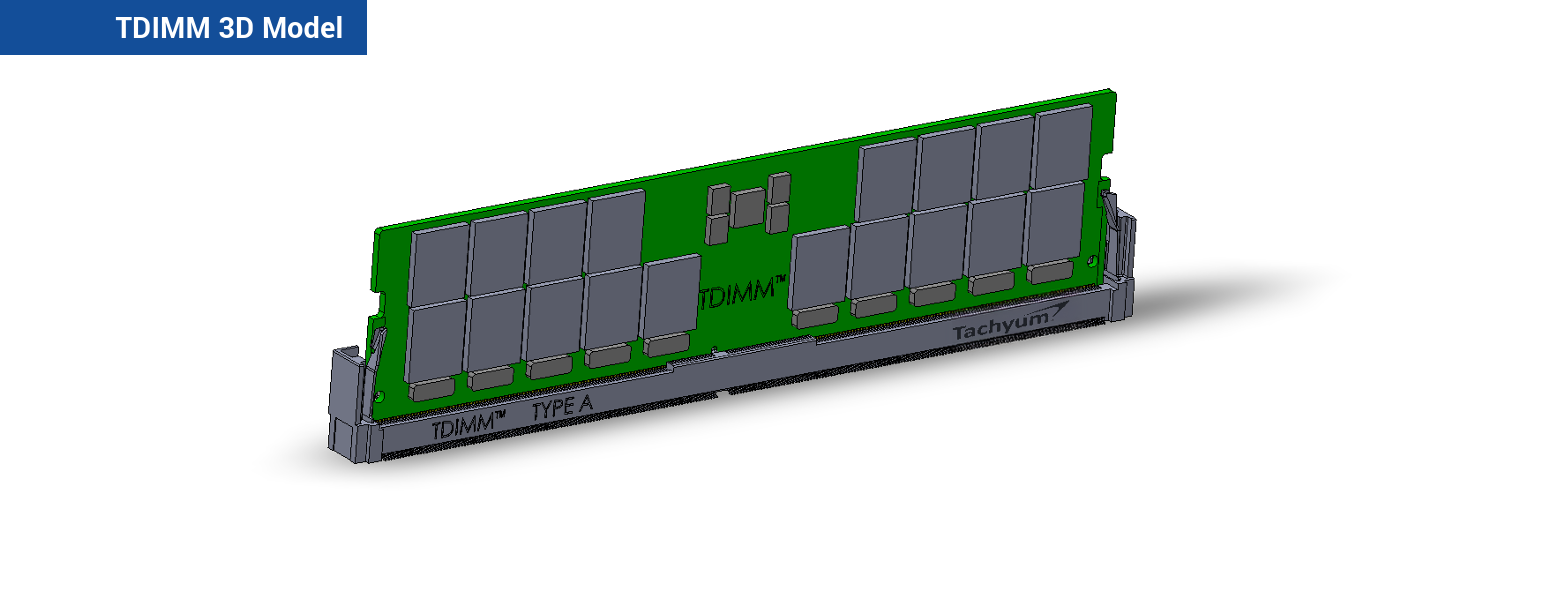

TDIMM steht fuer Tachyum DIMM und ist mehr als nur eine weitere Variante klassischer DDR5-Module. In heutigen Servern dominiert DDR5 RDIMM: 64 Bit Datenbus plus 16 Bit ECC, angebunden ueber einen 288-Pin-Steckplatz. Tachyum bricht dieses Schema auf und schlaegt einen 128 Bit breiten Datenbus mit weiterhin 16 Bit ECC vor, der ueber einen 484-Pin-Steckverbinder gefuehrt wird. Dazu kommt eine neu organisierte Signallandschaft mit angepassten DQS-Leitungen und Kontrollsignalen.

Der Effekt auf dem Papier ist spektakulaer: Laut Tachyum kann ein DDR5 TDIMM rund 281 GB/s liefern, waehrend ein typisches DDR5 RDIMM bei ungefaehr 51 GB/s liegt. Das entspricht grob einer Verfuenffachung der nutzbaren Bandbreite pro Modul. Ein Teil dieses Zuwachses ergibt sich schlicht aus der verdoppelten Busbreite, der Rest aus Optimierungen bei Signalführung und Protokoll-Overhead. Gleichzeitig behauptet das Unternehmen, dass die Anzahl der Signale nur um etwa 38 Prozent steigt – also deutlich weniger als eine strikte Verdopplung.

Kapazitaet bis 1 TB pro DIMM und das Kostenargument

Neben der Bandbreite ruckt die Kapazitaet in den Vordergrund. Die Referenzdesigns fuer TDIMM sehen drei Stufen vor: Standardmodule mit 256 GB, hoeher aufgebaute Varianten mit 512 GB und ein Extra-Tall-Formfaktor, der bis zu 1 TB pro Modul ermoeglichen soll. Fuer Workloads wie grosse Sprachmodelle, In-Memory-Datenbanken oder Echtzeitanalytik koennte das einen massiven Unterschied bedeuten. Statt Parameter und Datensaetze permanent ueber das Netzwerk nachzuladen, laesst sich deutlich mehr lokal im Arbeitsspeicher halten.

Interessant ist, dass Tachyum das Ganze nicht als Luxusloesung versteht, sondern explizit mit geringeren Kosten wirbt. Durch die Organisation der Ranks und den breiteren Bus sollen fuer dieselbe Kapazitaet etwa 10 Prozent weniger DRAM-Chips noetig sein als bei einem vergleichbaren RDIMM-Design. In Summe spricht das Unternehmen von rund 10 Prozent niedrigeren Modulpreisen. Ob sich das in realen Stuecklisten und unter den Margevorgaben der DRAM-Hersteller bestaetigt, bleibt vorerst offen – aber das Argument ist klar: mehr Bandbreite, mehr Kapazitaet, geringerer Preis pro Gigabyte.

Neuer Stecker, neue Plattform – aber vertraute Gehaeuse

Die Kehrseite: TDIMM ist nicht rueckwaerts kompatibel. Ein 484-Pin-Steckverbinder und ein 128 Bit breiter Speicherkanal verlangen nach neuen Mainboards und Speichercontrollern in den CPUs. Tachyum versucht, die Hemmschwelle zu senken, indem die mechanischen Abmessungen an klassische DDR5-DIMMs angelehnt sind. Im Idealfall koennen bestehende Servergehaeuse, Luftfuehrungen und Kuehlkonzepte weiterverwendet werden, waehrend sich das Innenleben aendert.

Wer die Geschichte des Speichermarkts kennt, weiss allerdings, wie hoch die Hürde fuer neue Standards ist. Rambus, Fully-Buffered-DIMMs und diverse proprietaere Loesungen hatten auf Folien beeindruckende Vorteile, scheiterten aber an Komplexitaet, Lizenzmodellen oder schlichter Zurueckhaltung der OEMs. TDIMM muss also mehr liefern als nur schoene Blockdiagramme: belastbare elektrische Spezifikationen, klare Roadmaps und vor allem Hersteller, die Module in Stueckzahlen produzieren wollen.

Ausblick auf DDR6 und 27 TB/s pro System

Tachyum denkt den Ansatz ueber DDR5 hinaus. Heute erreichen High-End-Systeme mit DDR5 Speicherbandbreiten im Bereich von rund 6,7 TB/s, je nach Konfiguration. Mit DDR6 rechnet die Branche grob mit einer Verdopplung auf etwa 13,5 TB/s. Tachyum geht einen Schritt weiter und skizziert TDIMM-Varianten fuer DDR6, die in Summe bis zu 27 TB/s pro System liefern sollen – angepeilt fuer den Zeitraum um 2028. Diese Zahlen sind ambitioniert, aber sie treffen einen Nerv: KI-Workloads skalieren zunehmend nicht mehr nur mit FLOPS, sondern mit Speicherbandbreite.

Mehr lokale Bandbreite pro Sockel koennte komplexe Multisocket-Topologien und umstaendliche Memory-Pooling-Loesungen teilweise überfluessig machen. Statt Daten permanent ueber Hochgeschwindigkeitslinks zwischen Knoten zu schieben, wuerden deutlich mehr Parameter direkt im lokalen RAM liegen. Das verspricht geringere Latenzen, weniger Energieverlust in der Fabric und einfachere Software-Stacks – sofern die Hardware haelt, was sie verspricht.

Gigantische KI-Versprechen und holprige Formulierungen

Besonders kontrovers sind die Aussagen zu Kosten und Energieverbrauch grosser KI-Rechenzentren. Tachyum zeichnet das Bild eines hypothetischen OpenAI-Massstabs, der mit konventioneller Technik Investitionen in der Groessenordnung von mehreren Billionen US-Dollar und eine Leistungsaufnahme von rund 250.000 Megawatt verschlingen koennte. Mit Prodigy-CPUs und TDIMM-Modulen sollen diese Werte angeblich auf einige Dutzend Milliarden Dollar und wenige Hundert Megawatt schrumpfen.

Noch einen Schritt weiter geht die Firma mit der Behauptung, dass sich bis 2028 KI-Systeme, die auf praktisch allem schriftlich erzeugten Wissen der Menschheit trainieren, von geschaetzten acht Billionen Dollar und hunderten Gigawatt auf etwa 78 Milliarden Dollar und rund ein Gigawatt druecken liessen. Die Aussagen sind so grosszuegig formuliert, dass viele Branchenkenner sie eher als Vision oder Marketing-Pitch lesen. Begriffe wie geschaetzt oder Szenario tauchen kaum auf, was bei technisch versierten Lesern für hochgezogene Augenbrauen sorgt.

Reaktionen aus der Community: zwischen Faszination und Augenrollen

In Foren und Kommentarspalten ist die Reaktion entsprechend gemischt. Ein Teil der Community findet die Idee eines offenen, breiteren Kanals mit 1-TB-DIMMs durchaus spannend. Wer heute mit speichergebundenen KI-Workloads kaempft, weiss, wie frustrierend es ist, von der Bandbreite statt von der Rechenleistung begrenzt zu werden. Wenn ein Standard wie TDIMM wirklich von grossen DRAM- und Serverherstellern aufgegriffen wird, koennte das ein echter Hebel sein.

Gleichzeitig ist der Spott laut: Viele Nutzer weisen darauf hin, dass sich theoretische Bandbreiten sehr leicht hochrechnen lassen, waehrend reale Systeme an Signalqualitaet, EMV, thermischen Effekten und Kostenstrukturen scheitern. Andere fragen ganz trocken, ob Tachyum ueberhaupt ein einziges Serienprodukt im Markt hat oder ob alles bislang auf Renderbildern und PDF-Slides basiert. Der Tenor: Die Idee ist interessant, aber solange kein Board im Labor und kein Server im Rack steht, bleibt TDIMM ein Versprechen.

Was passieren muss, damit TDIMM relevant wird

Damit TDIMM mehr wird als eine Fussnote in der Geschichte der Speicherstandards, braucht es einen klaren Fahrplan. Tachyum muss funktionierende Prototypen mit Prodigy-CPUs und TDIMM-Controller zeigen, detaillierte elektrische Spezifikationen oeffentlich machen und Referenzdesigns fuer Mainboards bereitstellen. Im naechsten Schritt braucht es mindestens einen grossen Modulhersteller, der bereit ist, TDIMMs in nennenswerten Stueckzahlen zu fertigen, sowie einen Cloud-Anbieter oder ein KI-Labor, das sich auf einen Pilot-Cluster einlaesst.

Erst dann wird sich zeigen, ob die versprochenen 1-TB-DIMMs, der Faktor fuenf bei der Bandbreite und die drastischen Einsparungen bei Kosten und Energie realistisch sind oder im Bereich ambitionierter Folienkunst bleiben. Bis dahin bewegt sich TDIMM in einem schmalen Spannungsfeld: Es koennte eine echte Zeitenwende fuer speicherhungrige KI-Workloads einlaeuten – oder als weiteres Beispiel dafuer enden, wie schwer es neue Speicherstandards im konservativen Servermarkt haben.

1 kommentar

Thank you for your sharing. I am worried that I lack creative ideas. It is your article that makes me full of hope. Thank you. But, I have a question, can you help me?