Was bedeutet „3 nm“ wirklich? Moderne Chiptechnologien erklärt

Jede neue Chipgeneration wird mit großen Versprechen präsentiert: Smartphones mit „3-nm-Prozessoren“, Roadmaps mit „2 nm“ und Schlagzeilen über enorme Leistungs- und Effizienzsprünge. Klingt so, als ginge es um messbare Strukturen von wenigen Atomen Breite. Doch die Realität sieht anders aus: Heute steht „3 nm“ nicht für eine physikalische Größe, sondern für eine Technologiegeneration, ein Label, das Fortschritt symbolisiert, aber nicht den Messschieber ersetzt.

Als Nanometer noch Längen waren

Früher war es einfach: Der Name des Prozesses entsprach in etwa der Gate-Länge des Transistors, also dem winzigen Schalter, der Stromfluss steuert. Ein 90-nm-Prozess bedeutete Gates um die 90 Nanometer. Bei 45 nm war das Ganze schon halb so groß. Das brachte klare Vorteile: mehr Transistoren pro Fläche, höhere Taktraten und bessere Energieeffizienz. Ein direkter, greifbarer Maßstab für den technischen Fortschritt.

Doch spätestens mit 28 nm brach dieses Modell zusammen. Transistoren wurden dreidimensional, und dutzende Parameter spielten eine Rolle: Gate-Länge, Fin-Höhe, Metall-Pitch, Kontaktabstände. Kein einzelner Wert spiegelte die Komplexität mehr wider.

Marketing statt Messschieber

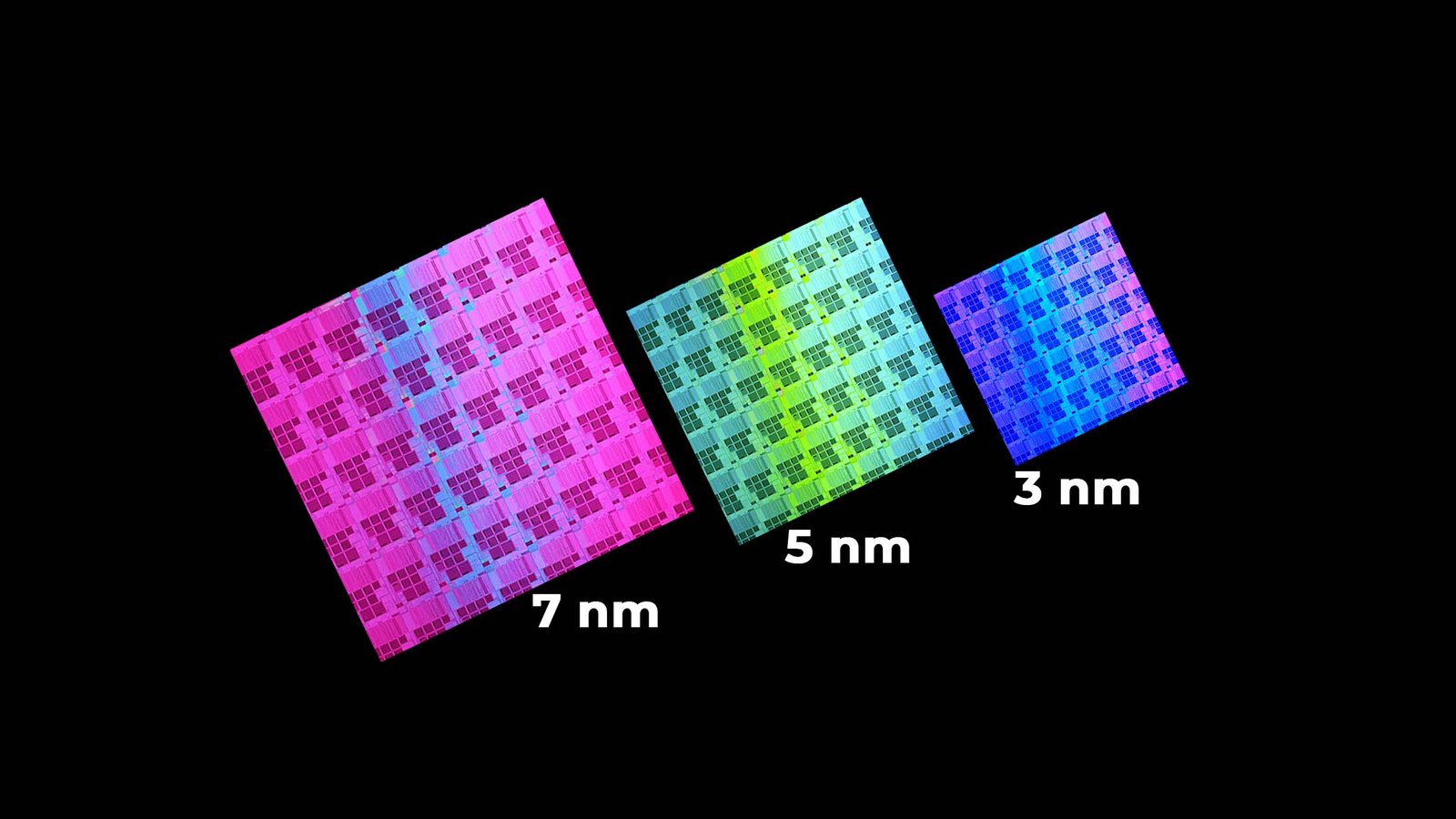

Statt Nanometer ganz zu streichen, machten Hersteller daraus Marketingnamen. „7 nm“, „5 nm“ oder „3 nm“ bedeuten nicht mehr wörtliche Maße, sondern: neues Design-Regelwerk, dichtere Strukturen, verbesserte Performance. In Wirklichkeit sind Bauteile moderner Transistoren 15 bis 30 nm groß – also weit entfernt von der Zahl auf dem Datenblatt. Man kann es mit Automodellen vergleichen: Ein BMW 3er ist nicht drei Meter breit, sondern steht für eine Generation.

Was „3 nm“ tatsächlich verspricht

- Dichte: Mehr Transistoren auf gleichem Raum, was komplexere Schaltungen ermöglicht.

- Performance: Höhere Taktfrequenzen, schnellere Schaltzeiten.

- Energieeffizienz: Weniger Verbrauch bei gleicher Leistung oder mehr Leistung ohne Mehrverbrauch.

Die „3 nm“-Bezeichnung ist damit eher ein Hinweis auf den technologischen Reifegrad. Hersteller wie TSMC, Samsung oder Apple wollen damit aussagen: Diese Generation bietet spürbare Fortschritte, auch wenn kein Transistor wirklich drei Nanometer misst.

Von Planar über FinFET zu GAAFET

Die Ära der planaren Transistoren endete mit dem Aufstieg der FinFETs. Hier steht ein dünner Siliziumfinnen-Kanal, den das Gate von drei Seiten umschließt. Die nächste Evolutionsstufe sind GAAFETs (Gate-All-Around), bei denen das Gate den Kanal komplett umgibt. Das reduziert Leckströme und ermöglicht eine feinere Abstimmung von Leistung und Verbrauch. Diese Architektur wird mit den kommenden „2-nm“-Nodes assoziiert.

Die Rolle der Interconnects

Transistoren allein sind nicht das einzige Problem. Metallleitungen, die Milliarden Transistoren verbinden, verursachen Verzögerungen und Energieverluste. Deshalb optimieren neue Prozesse auch die Interconnects: mehr Lagen, engere Abstände, neue Materialien. Eine zentrale Neuerung ist die Stromversorgung von der Rückseite („backside power delivery“), die Verluste reduziert und Platz auf der Oberseite schafft.

Warum Vergleiche hinken

Ein „3 nm“-Prozess von TSMC ist nicht direkt mit einem „3 nm“ von Samsung oder Intel vergleichbar. Jeder Hersteller definiert eigene Designregeln, optimiert für unterschiedliche Kunden – mal für Smartphones mit langer Akkulaufzeit, mal für Server mit maximaler Rechenleistung. Sogar innerhalb eines Nodes gibt es Varianten: stromsparend, dichteoptimiert oder für Hochleistung.

Was bedeutet das für Nutzer?

Für Smartphone-Käufer heißt „3 nm“ meist längere Akkulaufzeit und weniger Hitzeentwicklung. In Notebooks oder Rechenzentren bedeutet es mehr Kerne oder höhere Takte im gleichen Leistungsbudget. Am Anfang sind neue Prozesse teurer und schwerer herzustellen, mit der Zeit reifen sie und werden zur Norm, während ältere Nodes in günstigere Geräte wandern.

Blick nach vorn: 2 nm und mehr

Die Roadmaps zeigen bereits 2-nm-Technologien mit GAAFETs, stärkerem Einsatz von EUV-Lithografie und vor allem Advanced Packaging. Chiplets, 2.5D-Interposer, Hybrid-Bonding und 3D-Stacking werden die Zukunft prägen. Das Konzept nennt sich DTCO (Design-Technology Co-Optimization) und STCO (System-Technology Co-Optimization): Fortschritt entsteht aus dem Zusammenspiel von Transistor-, Interconnect- und Packaging-Innovationen.

Fazit

„3 nm“ ist kein Linealmaß. Es ist ein Etikett für eine neue Generation von Technologien, die Chips leistungsfähiger, effizienter und dichter machen. Die eigentliche Innovation steckt in Architekturen wie GAAFET, in neuen Versorgungstechniken und im Packaging. Solange die Industrie diese Hebel nutzt, bleibt das Fortschreiten der Node-Labels ein sinnvoller Orientierungspunkt – auch wenn die Zahl selbst längst nichts mehr mit einem realen Nanometer zu tun hat.

2 kommentare

Sehr guter Artikel, hätte gern noch was zu SRAM gelesen

Mir reicht längere Akkulaufzeit, Peaks brauch ich nicht 😂